Publications

Please check for Google Scholar.

2025

- J13

ZlibBoost: An Efficient and Flexible Open-Source Framework for Standard Cell CharacterizationACM Transactions on Design Automation of Electronic Systems, 2025

ZlibBoost: An Efficient and Flexible Open-Source Framework for Standard Cell CharacterizationACM Transactions on Design Automation of Electronic Systems, 2025 - J12

SenHDC: A 3-D NAND Flash-Based Processing-in-Sensor Hyperdimensional Computing ArchitectureIEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2025

SenHDC: A 3-D NAND Flash-Based Processing-in-Sensor Hyperdimensional Computing ArchitectureIEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2025 - C25

Deploying Edge LLMs for Wafer Defect Detection in Chip ManufacturingIn 2025 International Symposium of Electronics Design Automation (ISEDA), 2025

Deploying Edge LLMs for Wafer Defect Detection in Chip ManufacturingIn 2025 International Symposium of Electronics Design Automation (ISEDA), 2025 - C24

An Efficient Single-Cell Associative Search Engine via Conditional ExecutionIn 2025 International Symposium of Electronics Design Automation (ISEDA), 2025

An Efficient Single-Cell Associative Search Engine via Conditional ExecutionIn 2025 International Symposium of Electronics Design Automation (ISEDA), 2025 - C23

FactorHD: A Hyperdimensional Computing Model for Multi-Object Multi-Class Representation and FactorizationIn 2025 62nd ACM/IEEE Design Automation Conference (DAC), 2025

FactorHD: A Hyperdimensional Computing Model for Multi-Object Multi-Class Representation and FactorizationIn 2025 62nd ACM/IEEE Design Automation Conference (DAC), 2025 - C22

VQT-CiM: Accelerating vector quantization enhanced transformer with ferroelectric compute-in-memoryIn 2025 62nd ACM/IEEE Design Automation Conference (DAC), 2025

VQT-CiM: Accelerating vector quantization enhanced transformer with ferroelectric compute-in-memoryIn 2025 62nd ACM/IEEE Design Automation Conference (DAC), 2025 - J11

ANAS: Software-hardware co-design of approximate neural network accelerators via neural architecture searchIntegration, 2025

ANAS: Software-hardware co-design of approximate neural network accelerators via neural architecture searchIntegration, 2025 - J10

NeFT: negative feedback training to improve robustness of compute-in-memory DNN acceleratorsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025

NeFT: negative feedback training to improve robustness of compute-in-memory DNN acceleratorsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025 - J9

Empirical guidelines for deploying llms onto resource-constrained edge devicesACM Transactions on Design Automation of Electronic Systems, 2025

Empirical guidelines for deploying llms onto resource-constrained edge devicesACM Transactions on Design Automation of Electronic Systems, 2025 - C21

Hardware-Aware Compilation and Simulation for In-Memory ComputingIn 2025 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), 2025

Hardware-Aware Compilation and Simulation for In-Memory ComputingIn 2025 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), 2025 - C20

Tiny-Align: Bridging Automatic Speech Recognition and Large Language Model on EdgeIn 2025 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2025

Tiny-Align: Bridging Automatic Speech Recognition and Large Language Model on EdgeIn 2025 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2025 - C19

FACAM: Design and Optimization of A Compact Energy Efficient FeFET-Based Analog Content Addressable MemoryIn 2025 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2025

FACAM: Design and Optimization of A Compact Energy Efficient FeFET-Based Analog Content Addressable MemoryIn 2025 IEEE/ACM International Conference On Computer Aided Design (ICCAD), 2025 - J8

QUNF+: A Quadratic Approximation Framework with Hardware Co-Design for Universal Nonlinear Function Acceleration in Neural NetworksIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025

QUNF+: A Quadratic Approximation Framework with Hardware Co-Design for Universal Nonlinear Function Acceleration in Neural NetworksIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2025 - C18

Boosting Standard Cell Library Characterization with Machine Learning2025 30th Asia and South Pacific Design Automation Conference (ASP-DAC), 2025

Boosting Standard Cell Library Characterization with Machine Learning2025 30th Asia and South Pacific Design Automation Conference (ASP-DAC), 2025 - C17

Algorithm-Hardware Co-design of a Unified Accelerator for Non-linear Functions in TransformersIn 2025 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2025

Algorithm-Hardware Co-design of a Unified Accelerator for Non-linear Functions in TransformersIn 2025 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2025 - C16

NVCiM-PT: An NVCiM-assisted Prompt Tuning Framework for Edge LLMsIn 2025 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2025

NVCiM-PT: An NVCiM-assisted Prompt Tuning Framework for Edge LLMsIn 2025 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2025 - C15

A 10.60 μW 150 GOPS Mixed-Bit-Width Sparse CNN Accelerator for Life-Threatening Ventricular Arrhythmia Detection2025 30th Asia and South Pacific Design Automation Conference (ASP-DAC), 2025

A 10.60 μW 150 GOPS Mixed-Bit-Width Sparse CNN Accelerator for Life-Threatening Ventricular Arrhythmia Detection2025 30th Asia and South Pacific Design Automation Conference (ASP-DAC), 2025

2024

- J7

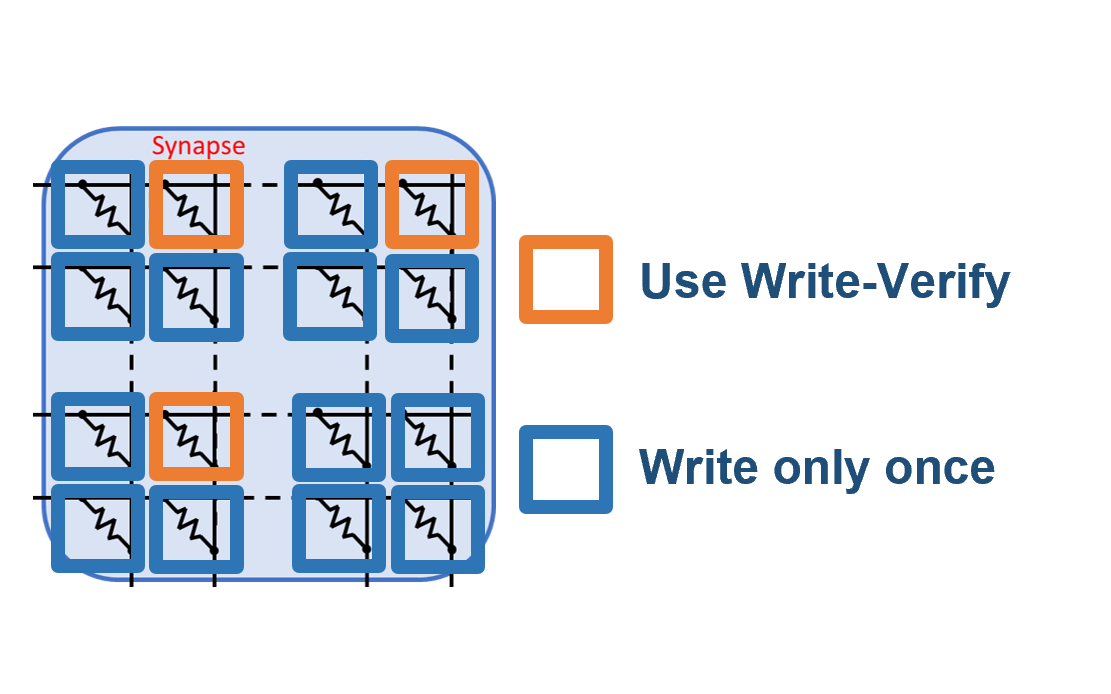

U-SWIM: Universal Selective Write-Verify for Computing-in-Memory Neural AcceleratorsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024

U-SWIM: Universal Selective Write-Verify for Computing-in-Memory Neural AcceleratorsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024 - J6

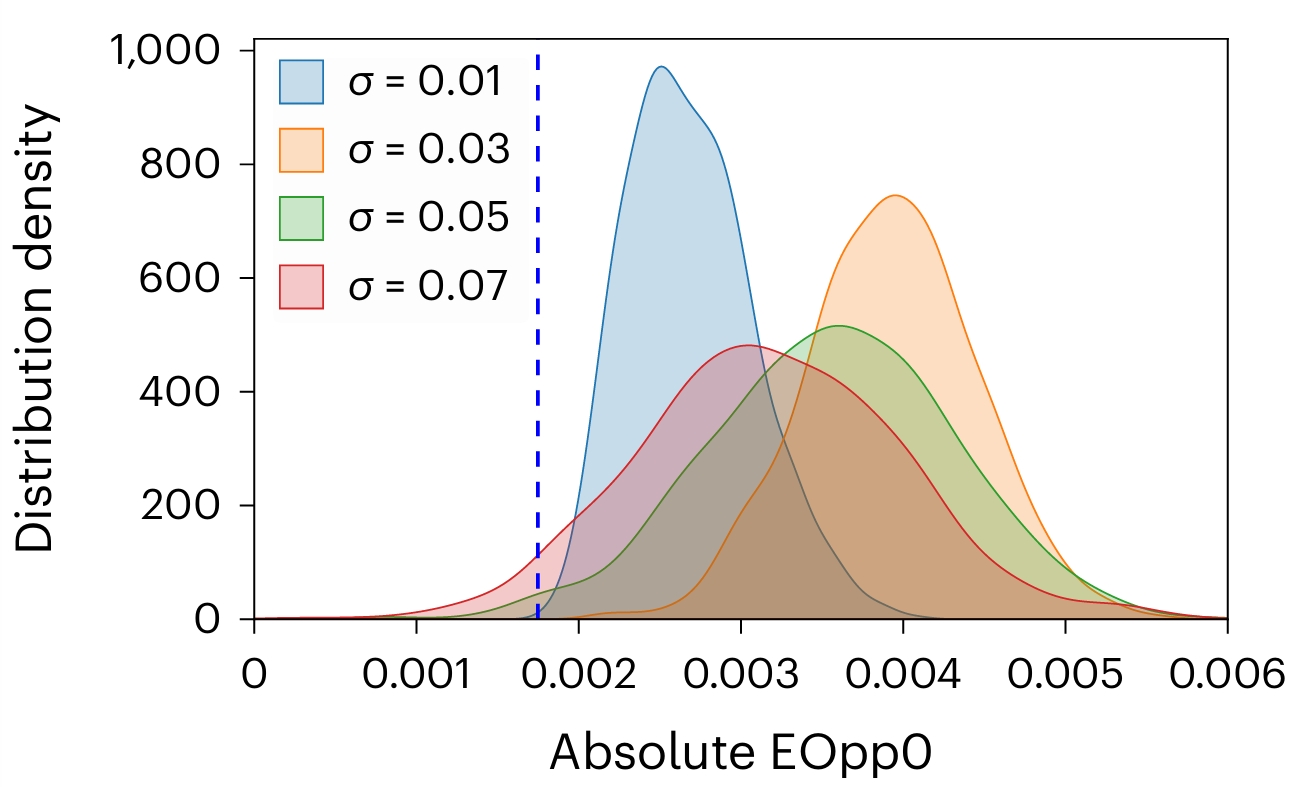

Hardware Design and the Fairness of A Neural NetworkNature Electronics, 2024

Hardware Design and the Fairness of A Neural NetworkNature Electronics, 2024 - J5

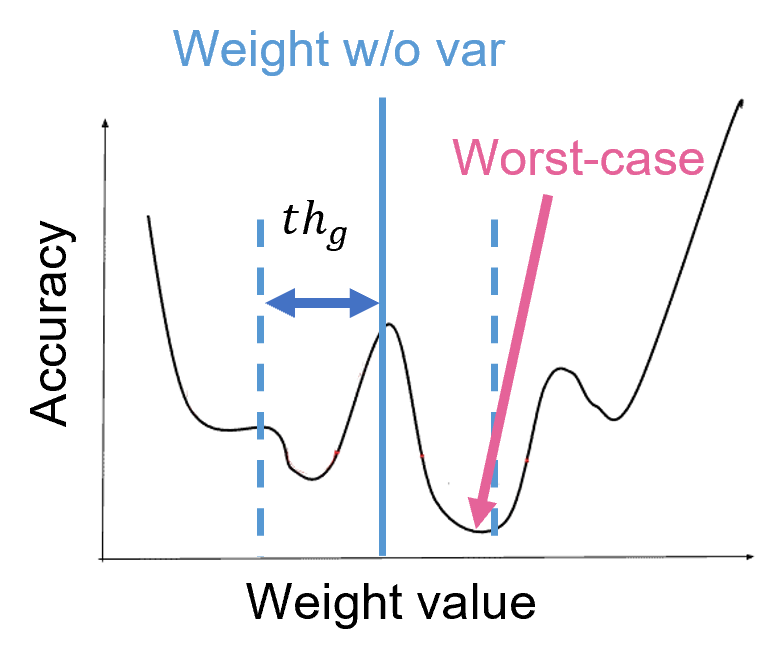

Compute-in-Memory based Neural Network Accelerators for Safety-Critical Systems: Worst-Case Scenarios and ProtectionsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024

Compute-in-Memory based Neural Network Accelerators for Safety-Critical Systems: Worst-Case Scenarios and ProtectionsIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024 - C14

Towards Fairness of Neural Architecture Search via LLMsIn 2024 29th Asia and South Pacific Design Automation Conference (ASP-DAC), 2024

Towards Fairness of Neural Architecture Search via LLMsIn 2024 29th Asia and South Pacific Design Automation Conference (ASP-DAC), 2024 - J4

Personalized Meta-Federated Learning for IoT-Enabled Health MonitoringIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024

Personalized Meta-Federated Learning for IoT-Enabled Health MonitoringIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024 - C12

TSB: Tiny Shared Block for Efficient DNN Deployment on NVCIM Accelerators2024 International Conference on Computer-Aided Design (ICCAD), 2024

TSB: Tiny Shared Block for Efficient DNN Deployment on NVCIM Accelerators2024 International Conference on Computer-Aided Design (ICCAD), 2024 - C11

Special Session: Sustainable Deployment of Deep Neural Networks on Non-Volatile Compute-in-Memory AcceleratorsIn 2024 International Conference on Hardware/Software Codesign and System Synthesis (CODES+ ISSS), 2024

Special Session: Sustainable Deployment of Deep Neural Networks on Non-Volatile Compute-in-Memory AcceleratorsIn 2024 International Conference on Hardware/Software Codesign and System Synthesis (CODES+ ISSS), 2024 - J3

CSA-CiM: Enhancing Multi-Functional Computing-in-Memory With Configurable Sense AmplifiersIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2024

CSA-CiM: Enhancing Multi-Functional Computing-in-Memory With Configurable Sense AmplifiersIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2024

2023

- C10

On the Viability of Using LLMs for SW/HW Co-Design: An Example in Designing CiM DNN AcceleratorsIn Proceedings of the 36th IEEE International System-on-chip Conference, 2023

On the Viability of Using LLMs for SW/HW Co-Design: An Example in Designing CiM DNN AcceleratorsIn Proceedings of the 36th IEEE International System-on-chip Conference, 2023 - B2

Hardware–Software Co-design of Deep Neural Architectures: From FPGAs and ASICs to Computing-in-MemoriesIn Embedded Machine Learning for Cyber-Physical, IoT, and Edge Computing: Software Optimizations and Hardware/Software Codesign, 2023

Hardware–Software Co-design of Deep Neural Architectures: From FPGAs and ASICs to Computing-in-MemoriesIn Embedded Machine Learning for Cyber-Physical, IoT, and Edge Computing: Software Optimizations and Hardware/Software Codesign, 2023 - C8

DASALS: Differentiable Architecture Search-Driven Approximate Logic Synthesis2023 International Conference on Computer-Aided Design (ICCAD), 2023

DASALS: Differentiable Architecture Search-Driven Approximate Logic Synthesis2023 International Conference on Computer-Aided Design (ICCAD), 2023

2022

- C6

Computing In Memory Neural Network Accelerators for Safety-Critical Systems: Can Small Device Variations Be Disastrous?2022 International Conference on Computer-Aided Design (ICCAD), 2022

Computing In Memory Neural Network Accelerators for Safety-Critical Systems: Can Small Device Variations Be Disastrous?2022 International Conference on Computer-Aided Design (ICCAD), 2022 - C5

Radars: memory efficient reinforcement learning aided differentiable neural architecture searchIn 2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC), 2022

Radars: memory efficient reinforcement learning aided differentiable neural architecture searchIn 2022 27th Asia and South Pacific Design Automation Conference (ASP-DAC), 2022 - B1

On the Reliability of Computing-in-Memory Accelerators for Deep Neural NetworksIn System Dependability and Analytics: Approaching System Dependability from Data, System and Analytics Perspectives, 2022

On the Reliability of Computing-in-Memory Accelerators for Deep Neural NetworksIn System Dependability and Analytics: Approaching System Dependability from Data, System and Analytics Perspectives, 2022 - C4

A Semi-Decoupled Approach to Fast and Optimal Hardware-Software Co-Design of Neural AcceleratorsTinyML Summit, 2022

A Semi-Decoupled Approach to Fast and Optimal Hardware-Software Co-Design of Neural AcceleratorsTinyML Summit, 2022 - J2

VisualNet: An End-to-End Human Visual System Inspired Framework to Reduce Inference Latency of Deep Neural NetworksIEEE Transactions on Computers, 2022

VisualNet: An End-to-End Human Visual System Inspired Framework to Reduce Inference Latency of Deep Neural NetworksIEEE Transactions on Computers, 2022

2021

- C3

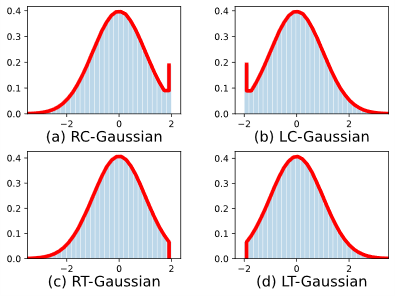

Uncertainty modeling of emerging device based computing-in-memory neural accelerators with application to neural architecture searchIn 2021 26th Asia and South Pacific Design Automation Conference (ASP-DAC), 2021

Uncertainty modeling of emerging device based computing-in-memory neural accelerators with application to neural architecture searchIn 2021 26th Asia and South Pacific Design Automation Conference (ASP-DAC), 2021

2020

- C2

Co-exploration of neural architectures and heterogeneous asic accelerator designs targeting multiple tasksIn 2020 57th ACM/IEEE Design Automation Conference (DAC), 2020

Co-exploration of neural architectures and heterogeneous asic accelerator designs targeting multiple tasksIn 2020 57th ACM/IEEE Design Automation Conference (DAC), 2020 - J1

Device-circuit-architecture co-exploration for computing-in-memory neural acceleratorsIEEE Transactions on Computers, 2020

Device-circuit-architecture co-exploration for computing-in-memory neural acceleratorsIEEE Transactions on Computers, 2020 - C1

When single event upset meets deep neural networks: Observations, explorations, and remediesIn 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), 2020

When single event upset meets deep neural networks: Observations, explorations, and remediesIn 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), 2020